# MONOTONICITY OF DIGITALLY CALIBRATED CYCLIC A/D CONVERTERS

János MÁRKUS Advisor: István KOLLÁR

### I. Introduction

Analog-to-digital converter designers are always searching for new converter structures, which have advantageous properties compared to their predecessors (e.g. higher resolution, higher speed, or lower power consumption).

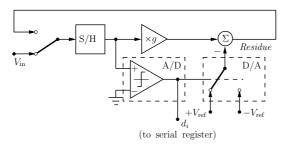

Figure 1: Block diagram of a cyclic converter.  $V_{\rm in}$ : input signal,  $V_{\rm ref}$ : reference signal, g: radix number (g=2 in an ideal case),  $d_i$ : one-bit digital output.

Cyclic converters, which form a special group within the 1-bit/stage sub-ranging converters, are easy to design, and they are good candidates to achieve very small power- and area consumption. Fig. 1 shows the block diagram of such a converter. Its operation is as follows. In the first cycle, the input signal is sampled and quantized by a one-bit A/D, then the quantized signal is converted to analog again by the D/A and subtracted from the input, which is multiplied by the radix number g (g = 2 in an ideal case). In the next cycle, this residue is used as an input signal to obtain the second MSB, and so on, up to n. The output of the converter (the

sequence of  $d_i$ ) is the binary representation of the input signal in an ideal case.

Due to analog component mismatches, the radix number g becomes inaccurate, and thus the resolution of these converters is limited to 10-12 bit using standard technologies. To enhance the resolution, digital self-calibration can be used [1,2]. Note that if g is inaccurate, two types of error exist [1]. If g>2, at specific inputs at least one stage will be saturated, causing *missing-decision-level* error (i.e., the output does not change for a wide range of the input signal). If g<2, *missing codes* will be introduced in the output (i.e., the output jumps for a small change in the input signal). Note that digital calibration, which simply reassigns the digital codes to another ones, does not correct for the first type of errors, thus a nominal g<2 must be used in these converters, and more stages must be used to compensate for the resolution loss [1,2].

In the next section it is shown that all sub-ranging converters with g < 2 produce non-monotonic output. A method to avoid this behaviour is also suggested.

## II. Monotonicity of the Converters

As noted in the previous section, in an ideal case, when g=2, the  $d_i$  output sequence of the converter is the binary representation of the input signal. By using a nominal gain g<2, however, the output sequence becomes radix-g based, i.e., the output can be calculated as [2,3]

$$D = \sum_{i=0}^{n-1} g^i d_i', (1)$$

where  $d'_0$  is the LSB and  $d'_{n-1}$  is the MSB value of the digital word.

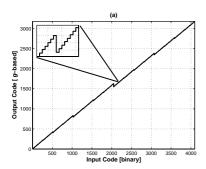

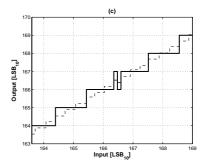

Figure 2: Different outputs of an n=12-cycle, g=1.95 cyclic converter. (a) All possible outputs of Eq. (1). (b) Real outputs of the converter. (c) 10-bit non-monotonic output example (dashed line: 12-bit code, solid line: 10-bit requantized code).

Calculating all possible codes with Eq. (1) results in huge non-monotonic jumps in the output (Fig. 2(a)). In reality, as discussed in the introduction, a cyclic converter with g < 2 exhibits missing codes. In addition, based on the converter's operation, it can be shown [3] that the absolute difference between the input signal and its radix-based representation (Eq. (1)) is always less then or equal to one LSB. Although this behaviour ensures that the difference between two consecutive digital outputs is less then or equal to one LSB, it allows this difference to be negative, thus, it allows non-monotonic behaviour, if such difference exists. It can be shown [3] that for any  $g \in (1,2)$  such code transition always exists. For example, if g = 1.95, then code transition xxxxxxxx100000 causes a negative step of -0.431 LSB. Such an example is enlarged in the inset of Fig. 2(b).

As noted in the introduction, using g < 2 causes resolution loss, thus more stages must be used for a given resolution. In other words, the calculated output code (cf. Eq. (1)) must be requantized to  $n_{\rm bit} \leq n-2$  bit [2]. Thus, the final LSB size will be 2–3 times larger then the step size of the radix-based converter, smoothing out most of the non-monotonic transitions. However, it can be shown [3] that there will always be some negative code transitions which crosses one of the (re)quantization thresholds, causing non-monotonic behaviour even in the final output. Such an example is depicted in Fig. 2(c).

In critical applications where this behaviour is not acceptable, it can be removed by a simple digital algorithm: in any cases where the 12-bit g=1.95-based output code contains 5 consecutive ones, subtracting one LSB, and where it contains 5 consecutive zeros, adding 1 LSB removes all the non-monotonic transitions while still maintains the same resolution.

### III. Conclusion

In this paper the non-monotonic property of digitally calibrated cyclic converters was introduced. It was shown that this behaviour always exists if the nominal gain (g) is less then two. A simple digital algorithm was suggested to ensure monotonicity. Both the theory and the solution can be extended to other 1-bit/stage sub-ranging converters with  $g \in (1, 2)$ .

## References

- [1] A. N. Karanicolas, H.-S. Lee, and K. L. Bacrania, "A 15-b 1-Msample/s digitally self-calibrated pipeline ADC," *IEEE Journal of Solid-State Circuits*, 28(12):1207–15, Dec. 1993.

- [2] O. E. Erdoğan, P. J. Hurst, and S. H. Lewis, "A 12-b digital-background-calibrated algorithmic ADC with -90-dB THD," *IEEE Journal of Solid-State Circuits*, 34(12):1812–20, Dec. 1999.

- [3] J. Márkus and I. Kollár, "On the monotonicity and maximum linearity of ideal radix-based A/D converters," in *IEEE Instrumentation and Measurement Technology Conference, IMTC*'2004, Como, Italy, 18–20 May 2004, submitted for publication.