## Ph.D. Thesis

János Márkus

BUDAPEST UNIVERSITY OF TECHNOLOGY AND ECONOMICS DEPARTMENT OF MEASUREMENT AND INFORMATION SYSTEMS

### Higher-order Incremental Delta-Sigma Analog-to-Digital Converters

by

János Márkus

M.S. (Budapest University of Technology and Economics) 1999

### A thesis

submitted to the Department of Measurement and Information Systems and the Doctoral Committee of the Budapest University of Technology and Economics in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Ph.D.)

in

Electrical Engineering

Advisor: István Kollár Dr. Acad.

### © 2005 János Márkus

Budapest University of Technology and Economics

Department of Measurement and Information Systems

H-1117 Budapest, XI. Magyar Tudósok körútja 2.

Building I., Level E, Room E330.

Tel:  $+36\,1\,463\,3587,$  Fax:  $+36\,1\,463\,4112,$  Email: markus@mit.bme.hu

# Contents

| N            | yilat      | kozat   | (Declaration of Authorship)                               | VI           |

|--------------|------------|---------|-----------------------------------------------------------|--------------|

| $\mathbf{A}$ | bstra      | ıct     |                                                           | IX           |

| K            | ivona      | at (Ab  | stract in Hungarian)                                      | $\mathbf{X}$ |

| $\mathbf{G}$ | lossa      | ry of S | Symbols                                                   | XII          |

| Pı           | refac      | e       |                                                           | XVI          |

| 1            |            | roduct  |                                                           | 1            |

|              | 1.1<br>1.2 |         | g-to-digital Conversion for Measurement Applications      |              |

| <b>2</b>     | Inc        | rement  | $	an \Delta \Sigma \ {f A}/{f D} \ {f Converters}$        | 7            |

|              | 2.1        | First-  | order Incremental (Charge-balancing) Converter            | . 7          |

|              |            | 2.1.1   | Dual-slope Converter                                      | . 8          |

|              |            | 2.1.2   | Unipolar First-order Incremental Converter                | . 9          |

|              |            | 2.1.3   | Bipolar Operation                                         | . 13         |

|              |            | 2.1.4   | Implementation Details                                    | . 16         |

|              | 2.2        | Exten   | sions of the First-order Converter                        | . 18         |

|              |            | 2.2.1   | Refining the Quantization Noise                           | . 18         |

|              |            | 2.2.2   | Using Different Architecture                              | . 19         |

|              |            | 2.2.3   | Higher-order Modulators                                   | . 20         |

| 3            | Ext        | ension  | s to Higher-order Architectures                           | 21           |

|              | 3.1        | First-  | order Modulator with Higher-order Filtering               | . 21         |

|              |            | 3.1.1   | Analysis of Higher-order Filters                          | . 23         |

|              |            | 3.1.2   | Analysis of the Dither Signal                             |              |

|              |            | 3.1.3   | Simulation Results                                        | . 29         |

|              | 3.2        | Possil  | ole Extensions to Higher-order Modulators                 | . 32         |

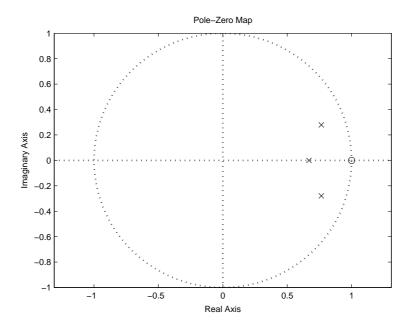

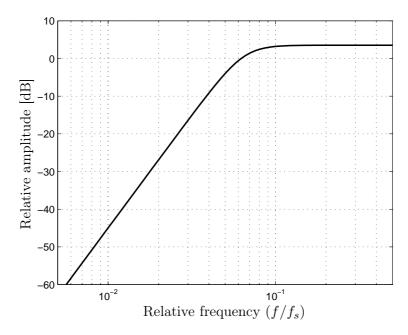

|              |            | 3.2.1   | Modulators with Pure Differential Noise Transfer Function | . 32         |

|              |            | 3.2.2   | Matched Digital Filters                                   | . 41         |

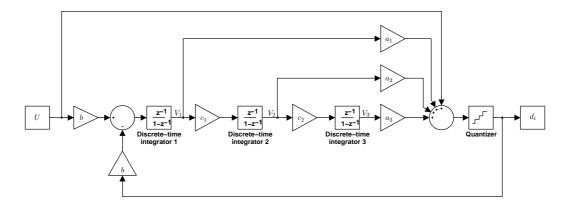

|              |            | 3.2.3   | Using Cascaded-Integrators, Feed-Forward (CIFF) Structure | . 43         |

|              |            | 3.2.4   | Comparison of the Two Extensions                          | . 59         |

VI CONTENTS

| 4       | Pro   | perties of Higher-order Structures                                      | 61  |

|---------|-------|-------------------------------------------------------------------------|-----|

|         | 4.1   | Behavior with Constant Input and Additive Noise                         | 61  |

|         |       | 4.1.1 Constant Input with Additive Gaussian Noise                       | 61  |

|         |       | 4.1.2 Constant Input with Periodic Noise                                | 67  |

|         |       | 4.1.3 General Case                                                      | 67  |

|         | 4.2   | Line Frequency Suppression                                              | 69  |

|         |       | 4.2.1 Modulators with Pure Differential Noise Transfer Function         | 71  |

|         |       | 4.2.2 CIFF Modulators with Stabilized Noise Transfer Function           | 83  |

|         |       | 4.2.3 Optimized Line Frequency Suppression                              | 90  |

|         | 4.3   | Practical Considerations                                                | 93  |

|         |       | 4.3.1 Offset and Asymmetry Errors                                       | 93  |

|         |       | 4.3.2 Input Scaling and Gain Error                                      | 95  |

|         |       | 4.3.3 Finite Op-amp Gain and Bandwidth                                  | 96  |

|         |       | 4.3.4  kT/C Noise                                                       | 97  |

|         |       | 4.3.5 Op-amp Nonlinearity                                               | 97  |

|         |       | 4.3.6 Capacitor Nonlinearity                                            | 97  |

|         |       | 4.3.7 Multi-bit Quantization                                            | 98  |

| 5       | Des   | sign Examples                                                           | 101 |

|         | 5.1   | Selection Guide                                                         | 101 |

|         | 5.2   | First-order Converters                                                  | 102 |

|         | 5.3   | Higher-order Converters                                                 | 104 |

|         |       | 5.3.1 Design Considerations                                             | 104 |

|         |       | 5.3.2 Modulators with Pure Differential Noise Transfer Function         | 106 |

|         |       | 5.3.3 One-bit CIFF Modulators with Stabilized Noise Transfer Function . | 108 |

|         | 5.4   | Experimental Results                                                    | 109 |

| 6       | Out   | clook                                                                   | 111 |

|         | 6.1   | Further Analysis of the Proposed Structures                             | 111 |

|         | 6.2   | Possible Future Architectures                                           |     |

| Bi      | bliog | graphy                                                                  | 114 |

| ${f A}$ | Ori   | ginal Contributions                                                     | 121 |

|         |       |                                                                         | 127 |

| ப       | TIPL  | Of I ubilications                                                       | 141 |

### Nyilatkozat (Declaration of Authorship)

Alulírott Márkus János kijelentem, hogy ezt a doktori értekezést magam készítettem és csak a megadott forrásokat használtam fel. Minden olyan részt, amelyet szó szerint, vagy azonos tartalomban, de átfogalmazva más forrásból átvettem, egyértelműen, a forrás megadásával megjelöltem.

A dolgozat bírálatai és a védésről készült jegyzőkönyv a későbbiekben a Budapesti Műszaki és Gazdaságtudományi Egyetem Villamosmérnöki és Informatikai Karának dékáni hivatalában lesz elérhető.

Budapest, 2005. március 9.

Márkus János jelölt

#### **Abstract**

### János Márkus "Higher-order Incremental Delta-Sigma Analog-to-Digital Converters" PhD thesis

Analog-to-digital conversion, which takes continuous-time, continuous amplitude signals (voltage, temperature, sound, etc.) and converts them into a series of numbers to be used for digital signal processing, is becoming the key element of the scholarly and industrial applications of measurement and data acquisition, and A/D converters are surrounding (though invisible in most cases) our everyday life.

In instrumentation and measurement, there is a growing demand for A/D converters with low or medium bandwidth, but with high absolute accuracy (e.g., sensors, demeasurement applications). High linearity and small offset are also among the requirements, as well as small power-consumption and low sensitivity to environmental noise (such as the periodic noise coupled from the mains or digital switching noise). One solution to the problem is the incremental (or charge-balancing)  $\Delta\Sigma$  converter, which is basically a first-order  $\Delta\Sigma$  A/D converter, operated in transient mode. The converter represents a hybrid between the classical dual-slope converter and the  $\Delta\Sigma$  one.

This dissertation extends the operation of the incremental converter to higher-order  $\Delta\Sigma$  loops. It discusses the basic operation of such a converter, the theoretically achievable resolution, filter design methods for the digital filter following the  $\Delta\Sigma$  modulator, and the structure's sensitivity to analog circuit elements imperfections. The introduced general architecture is flexible, thus it is capable to optimize the trade-off between circuit complexity and conversion accuracy.

Design examples and optimization techniques are proposed to help designers selecting the best configuration for a given application. The thesis also compares the results with those found in the literature.

The theoretical results are verified by simulations and also by measurements made on an integrated circuit.

#### Kivonat (Abstract in Hungarian)

Márkus János "Többedrendű, számláló típusú Delta-Szigma analóg-digitális átalakítók" PhD értekezés

Az analóg-digitális (A/D) átalakítás, amelynek során egy analóg jelből (feszültség, hőmérséklet, hang stb.) számítógépes feldolgozásra alkalmas számsorozatot készítünk, egyre inkább kulcsfontosságú szerepet játszik a méréstechnika és adatgyűjtés ipari ill. tudományos alkalmazásaiban, ugyanakkor A/D átalakítók vesznek körül bennünket – bár többnyire észrevétlenül – a mindennapi életben is.

A műszer- és méréstechnikában sokszor van szükség olyan A/D átalakítóra, amelynek sávszélessége közepes vagy kicsi, viszont abszolút pontossága igen nagy (pl. szenzorok, DC-mérő alkalmazások). Sokszor követelmény ilyen alkalmazásoknál a kis linearitási hiba és az elhanyagolható ofszet is, továbbá a kis fogyasztás ill. zajérzéketlenség. Egy megoldás erre a feladatra a számláló típusú (incremental)  $\Delta\Sigma$  átalakító, amely az elsőrendű  $\Delta\Sigma$  A/D átalakító tranziens működéséből származtatható. Az átalakító egyfajta hibridet képez a klasszikus dual-slope és a  $\Delta\Sigma$  átalakító között.

A dolgozat az elsőrendű számláló típusú átalakító működését terjeszti ki magasabb rendű  $\Delta\Sigma$  modulátorokra. Tárgyalja a működés alapelveit, az elvileg elérhető felbontást, a modulátort követő digitális szűrő tervezési módszereit, illetve az áramköri elemek pontatlanságára való érzékenységet. Mivel a javasolt általános struktúra többféle modulátortípust magába foglal, így könnyen megtalálható a legjobb kompromisszum az áramköri bonyolultság illetve az átalakító pontossága, gyorsasága között.

Tervezési példák, valamint optimalizációs technikák segítik az ilyen átalakító tervezőjét a legjobb konfiguráció megtalálásában egy adott alkalmazás esetén. A dolgozat összehasonlító elemzést is végez az irodalomban fellelhető módszerekkel.

Az elért elméleti eredményeket szimulációk, valamint egy elkészült integrált áramkör mérési eredményei támasztják alá.

# Glossary of Symbols

### Symbols

| a                                | Coefficient of a $\Delta\Sigma$ modulator.                                               |

|----------------------------------|------------------------------------------------------------------------------------------|

| b                                | Scaling coefficient of a $\Delta\Sigma$ modulator at the input.                          |

| B                                | Bandwidth of an analog signal.                                                           |

| $c_i$                            | Scaling coefficient of a $\Delta\Sigma$ modulator.                                       |

| C                                | Capacitor.                                                                               |

| $d_i, D(z)$                      | Digital output of the modulator.                                                         |

| D(z)                             | Denominator of the $NTF$ of a stabilized $\Delta\Sigma$ modulator.                       |

| $D_{ m out}$                     | Digital output of the converter.                                                         |

| $\epsilon[k]$                    | Discrete-time step-function.                                                             |

| $\varepsilon[k], \varepsilon(z)$ | Quantization error of the A/D converter within the $\Delta\Sigma$ -loop in               |

|                                  | the sample- or z-domain. See also $q[k], q(z)$ .                                         |

| $f_{ m clk}$                     | Clock rate of an SC circuit in Hertz.                                                    |

| $f_N$                            | The minimum sampling rate required for the reversible conversion                         |

|                                  | of an analog signal with bandwidth $B, f_N = 2B$ . It is usually                         |

|                                  | referred as Nyquist-rate.                                                                |

| $f_s$                            | Sampling frequency.                                                                      |

| k                                | Boltzmann's constant, used in noise analysis. $k = 1.38 \cdot 10^{-23} \text{JK}^{-1}$ . |

|                                  | k is also used as general variable in other contexts.                                    |

| l                                | Number of levels of the internal quantizer and feedback DAC in a                         |

|                                  | $\Delta\Sigma$ modulator.                                                                |

| $L_a$                            | Order of the analog $\Delta\Sigma$ modulator.                                            |

| $L_d$                            | Order of the digital filter following the $\Delta\Sigma$ modulator.                      |

| m                                | Mean value of a stochastic signal. Used also as the number of                            |

|                                  | significant samples of an IIR-filter's impulse-response.                                 |

| N                                | Number of cycles through an incremental converter operates.                              |

| $n_{ m bit}$                     | Number of bits of an incremental converter.                                              |

| $N_i$                            | Decimation ratio of an $i$ th-order sinc-filter following a pure differ-                 |

|                                  | ential $\Delta\Sigma$ modulator.                                                         |

| $N_{i,p}$                        | Decimation ratio of an $i$ th-order sinc-filter following a $\Delta\Sigma$ modu-         |

|                                  | lator with stabilizing poles.                                                            |

| OSR                              | Oversampling ratio, $OSR = f_s/f_N = f_s/(2B)$ .                                         |

|                                  |                                                                                          |

| $\Phi_i$     | The $i$ th clock phase of a switched-capacitor circuit.                                 |

|--------------|-----------------------------------------------------------------------------------------|

| q[k], q(z)   | Quantization error of the $whole$ incremental $\Delta\Sigma$ A/D converter in           |

|              | the sample- or the z-domain. See also $\varepsilon[k], \varepsilon(z)$ .                |

| $\sigma$     | Standard deviation of a stochastic signal (also the rms-value for                       |

|              | signals with zero mean).                                                                |

| $\sigma^2$   | Variance of a stochastic signal.                                                        |

| $S_i$        | Switch no. $i$                                                                          |

| T            | Temperature in Kelvin, used for noise analysis.                                         |

| T            | Time.                                                                                   |

| $T_{ m clk}$ | Length of one period of a clock signal in seconds.                                      |

| u,u[k],U(z)  | Relative (normalized) input signal of the A/D converter, $u=$                           |

|              | $V_{\rm in}/V_{\rm ref}$ . $u$ stands for dc-signal, while $u[k]$ and $U(z)$ represents |

|              | general input signals in the sample- and $z$ -domain, respectively.                     |

| $U_{\max}$   | Maximum relative (normalized) input signal of the A/D converter,                        |

|              | $U_{ m max} = V_{ m max}/V_{ m ref}$ .                                                  |

| $V_d$        | Dither signal in volts.                                                                 |

| $V_{ m in}$  | Input signal of the A/D converter in volts.                                             |

| $V_{ m int}$ | Output of the integrator of the first-order incremental converter in                    |

|              | volts.                                                                                  |

| $V_{ m lsb}$ | Equivalent voltage of the LSB, $V_{\rm lsb} = 2V_{\rm max}/2^{n_{\rm bit}}$ .           |

| $V_{ m max}$ | Maximum input signal of the A/D converter in volts.                                     |

| $V_{ m ref}$ | Reference signal of the A/D converter in volts.                                         |

| w[k]         | Weighting function or impulse response.                                                 |

| $w_d[k]$     | Weighting function or impulse response of the IIR-filter $1/D(z)$ .                     |

|              |                                                                                         |

### Abbreviations

| A/D  | Analog-to-Digital                                                      |

|------|------------------------------------------------------------------------|

| ac   | Alternating current (in general: non-constant part of a signal)        |

| ADC  | Analog-to-Digital Converter                                            |

| CIC  | Cascaded-Integrators-Comb filter, efficient realization of the digital |

|      | sinc-filter.                                                           |

| CIFF | Cascaded-Integrators, Feed-forward $\Delta\Sigma$ architecture         |

| CMOS | Complementary Metal-Oxid-Semicondutor, today's most com-               |

|      | monly used implementation technology for digital integrated cir-       |

|      | cuits.                                                                 |

| CoI  | Cascade-of-Integrators digital filter.                                 |

| D/A  | Digital-to-Analog                                                      |

| DAC  | Digital-to-Analog Converter                                            |

| dB   | deci<br>Bell, logarithmic power-ratio. Used mainly for $SNR$ in this   |

|      | thesis.                                                                |

| dc   | Direct current (in general: constant part of a signal)                 |

$\Delta\Sigma$  Delta-Sigma modulation. This technique is often referred as

$\Sigma\Delta$  (Sigma-Delta) modulation. In this thesis, according to

[Norsworthy et al., 1997], the term  $\Delta\Sigma$  is used.

ENOB Effective or equivalent number of bits

FIR Finite impulse response

HF High frequency IC Integrated circuit

IIR Infinite impulse response

LF Low frequency

lhs Left hand side (of an expression)

LSB Least significant bit

MASH Multi-stage noise-shaping or cascaded  $\Delta\Sigma$  converter architecture

MSB Most significant bit

N/A Used as either Not Available or Not Applicable

NTF Noise transfer function, transfer function from the internal quan-

tizer to the output of a  $\Delta\Sigma$  modulator.

Nyquist-rate See  $f_N$  in symbols

OSR Oversampling ratio,  $OSR = f_s/f_N = f_s/(2B)$ .

RC-constant Time constant of an exponential settling determined by a resistor

(R) and capacitor (C).  $\tau = RC$ .

rhs Right hand side (of an expression)

rms Root mean square SC Switched-capacitor

$\Sigma\Delta$  See  $\Delta\Sigma$

sinc Sinc-function,  $\operatorname{sinc}(x) = \sin(\pi x)/\pi x$ .

$\operatorname{sinc}_d$  Discrete-time sinc-function,

$\operatorname{sinc}_d(x) = \operatorname{sinc}(Nx)/\operatorname{sinc}(x) = \sin(\pi Nx)/(N\sin(\pi x)), \text{ where } N \text{ is}$

the length of the discrete-time rectangle window.

SNR Signal-to-noise ratio. In this thesis this term is usually used for

Signal-to-quantization-noise ratio.

SoC System-on-a-Chip, technology to integrate all processing units,

memories and I/O circuits onto the same chip

STF Signal transfer function, transfer function from the input to the

output of a  $\Delta\Sigma$  modulator.

UGB Unity-gain bandwidth of an operational amplifier (op-amp).

### Preface

This thesis is the collection of the main results achieved in the field of  $\Delta\Sigma$  analog-to-digital conversion during my five years long research period conducted at the Budapest University of Technology and Economics (BUTE), Budapest, Hungary and at Oregon State University (OSU), Corvallis, Oregon, USA.

I have started my PhD studies in 1999, right after graduation, at the Department of Measurement and Information Systems (BUTE) under the supervision of Prof. István Kollár. During the first two years I have gained a lot of theoretical and practical knowledge, especially in Quantization Theory, Digital Signal Processing, Matrix Theory and test methods of Analog-to-Digital Converters. From March, 2001 I have spent 14 months as a visiting scholar at Oregon State University, where I was working under the supervision of Prof. Gábor C. Temes, from whom I learnt many aspects of Delta-Sigma modulation and analog circuit design theory and practice.

From Sept. 2002, after I returned to Hungary, I have finalized and prepared for publication the results achieved in the topic of delta-sigma analog-to-digital converters in Oregon. Due to the courses I had to finish as PhD student and various teaching and research activities, I finally started to write this thesis in summer, 2004 and finished it in its first form by the end of the same year.

I would like to thank the colleagues at both the mixed-signal research group at OSU and the Department of Measurement and Information Systems at BUTE for the inspiring environment and the useful discussions. First of all I would like to thank István Kollár, my advisor at BUTE for his help, ideas, feedback and encouragements. I would also like to thank Prof. Gábor C. Temes for my visit to Oregon, his continuous help, critical remarks and his emphasis on writing good technical papers. I thank José Silva, Un-ku Moon and many colleagues at BUTE (especially László Balogh, Balázs Bank, Károly Molnár, József Németh, László Sujbert, Zoltán Szabó, Balázs Vödrös) for their help and the useful discussions during coffee and lunch breaks. Many thanks go to Microchip Technology Inc. and the incremental project team for the circuit-level design and implementation of the prototype chip.

This thesis has been supported by the Faculty of Electrical Engineering and Informatics at BUTE, the NSF US-Hungary grant at OSU, the NSF CDADIC (Center for Design of Analog-Digital Integrated Circuits) project, the Panda Audio Ltd, the László Schnell Instrumentation and Measurement Foundation, the Siemens AG, the Lawrence Livermoore National Laboratory and by the Department of Measurement and Information Systems. I would like to thank for their financial support.

XVIII

Special thanks to my parents for their constant love and support. I would like to thank my wife, Johanna and child, Barnabás for their patience and understanding and for all the happiness they bring into my life. Finally, I would like to thank God, my heavenly father for the given talents and possibilities in my life, which made it possible to finish this PhD thesis.

### Chapter 1

### Introduction

In today's engineering technology almost every problem is solved using digital hardware. Digital hardware is more economical, less sensitive or even capable to adapt to the environmental changes and noise, easier to reconfigure or reuse, and in general it is more robust than its analog equivalents. It is true for scholarly and industrial applications (data acquisition, measurement, control loops, etc), as well as in commercial units (e.g., digital thermometer, compact disk, appliances, fuel injection control in vehicles, digital radio receiver, etc.). In order to work properly, most of these applications communicate with the real world through sensors and actuators. As the real world has analog (continuous-time, continuous amplitude) signals and digital hardware can only deal with numbers at a given clock-rate (discrete-time, discrete amplitude signals), every sensor must be accomplished with an analog-to-digital converter (A/D converter or ADC) and every actuator is driven by a digital-to-analog converter (D/A converter or DAC), which performs the required conversion between the analog and digital signals. This thesis focuses on A/D converter design methods.

Integrated A/D converter design started at the same time the first digital processing units become available in the second half of the 20th century (one of the first fully integrated converter was introduced in 1978 by [Hamadé, 1978]). Since then, numerous architecture have been developed, which can be classified many ways. One possible way is based on the ratio of the input signal bandwidth (B) and the converter's conversion rate, usually referred as sampling rate  $(f_s)$ . It is well known from the Nyquist-theory (see e.g., [Oppenheim and Schafer, 1975), that an analog signal with bandwidth B can be perfectly reconstructed from its sampled equivalent, if the sampling rate  $f_s$  is greater than (or equal to) twice the bandwidth of the signal, i.e.,  $f_s \geq 2B$ . Based on the relationship of  $f_s$  and B, converters may be divided into two categories: Nyquist-rate converters  $(f_s/(2B) = 1)$  or only slightly larger) and oversampling converters  $(f_s/(2B) \gg 1)$ . Typically, Nyquist-rate converters have one-to-one relationship between the instantaneous input signal and a single output value (sample-by-sample conversion). In the other case, oversampling converters operate at much higher rate than twice the signal bandwidth (Nyquist-rate), and the final output sequence is achieved by appropriate digital filtering and decimation. In this case one cannot find sample-by-sample relationships between the analog and digital data, only the waveform and its spectral properties are preserved during conversion.

Table 1.1: A/D converter requirements of different applications

| Application       | Requirements |           |             |  |

|-------------------|--------------|-----------|-------------|--|

|                   | Resolution   | Bandwidth | Power-      |  |

|                   |              |           | Consumption |  |

| Microcontrollers  | Low-Med      | Low-Med   | Low-Med     |  |

| LF Measurement    | High         | Low-Med   | Low-Med     |  |

| Sensor(-arrays)   | High         | Low-Med   | Low         |  |

| Audio             | High         | Med       | N/A or Low  |  |

| Control           | Med-High     | Low-Med   | N/A         |  |

| Video             | Med-High     | High      | N/A         |  |

| HF, microwave     | Med          | High      | N/A         |  |

| Telecommunication | Med          | High      | N/A or Low  |  |

Another way of classification is based on the bandwidth, resolution and power-consumption requirements of different applications. The most typical applications with requirements regarding to the A/D converters is listed in Tab. 1.1. These requirements are usually contradicted by each other: high resolution and high bandwidth indicates more complex hardware, which should have low power- and area-consumption (especially for portable, battery-operated equipment), and should have great tolerance on environmental effects (noise, temperature, etc.) at the same time. In addition, today's trend in system design is that the analog and mixed-signal interfaces are integrated into the same integrated circuit (IC) as the digital signal processing units (System-on-a-Chip, SoC design). This gives two serious limitations on high-resolution classical Nyquist-rate A/D converter design: first, in today's widely used low-voltage CMOS digital circuit implementation technology it is not possible to manufacture high-precision analog elements (resistors, capacitors, etc.) on which classical Nyquist-rate converters relies so much. Second, with such an integrated environment, designers have to deal with the switching-noise interference originating from the high-speed clock signal of the digital circuits. In general, as matching of analog elements cannot be made better than 0.1% (which indicates a signal to mismatch error ratio of 1000, equivalent of about 10 bit resolution), classical Nyquist-rate converters with resolution greater than 10 bits can be manufactured either with individual (and thus expensive) laser wafer trimming or has to be designed with sophisticated on-line or off-line self-calibration methods.

To overcome these problems, A/D converters based on Delta-Sigma ( $\Delta\Sigma$ ) or Sigma-Delta ( $\Sigma\Delta$ ) modulation can be a good candidate for high-resolution conversion in an integrated environment, especially if it is realized using switched-capacitor (SC) circuits. Switched-capacitor circuits can be modeled as discrete-time, continuous amplitude systems, and as the information in the circuit is stored in charges delivered in a given time-interval ( $T_{\rm clk}$ ) rather than voltage or current, it is less sensitive to pulse-like switching noise coupled from the digital part of the circuit. Another useful property of the SC circuits is that they rely only on capacitive matching which can be made as low as 0.1% with careful layout. This matching is about three orders better than the tolerance of the time constant of classical RC-circuits integrated in CMOS environment [Johns and Martin, 1997,

Telecommunication

Application Architecture Nyquist-rate Oversampling Microcontrollers Successive apprx., Algo-N/Arithmic/Cyclic dc, LF Measurement, Incremental  $\Delta\Sigma$ Dual-slope, Voltage-Biomedical app. to-frequency Sensor(-arrays) Dual-slope Incremental  $\Delta\Sigma$ Audio Successive apprx. simple oversampling,  $\Delta\Sigma$ N/A Control Successive apprx., Algorithmic/Cyclic low- $OSR \Delta \Sigma$ Video Flash, Pipelined HF, microwave Flash, Pipelined Bandpass  $\Delta\Sigma$

Flash, Successive apprx.

$\Delta\Sigma$

Table 1.2: Classification of different A/D converter architectures. Bold typeset indicates the architecture discussed in this thesis.

#### Chap. 10].

The advantage of using  $\Delta\Sigma$  modulation (first introduced by [Inose et al., 1962]) instead of classical Nyquist-rate conversion is that  $\Delta\Sigma$  modulator structures do not rely on precise analog elements, but they sample the incoming signal at a much higher rate than the bandwidth of the incoming signal (oversampling), and shape the quantization error of the low-resolution (often one-bit) quantizer by means of analog filtering (noise-shaping) [Norsworthy et al., 1997, Sec. 1.2], achieving high signal-to-noise ratio (SNR) in the signal band. The architecture is also capable to modulate most of the analog imperfection errors out of the band of interest. The oversampled signal is converted back to Nyquist-rate by means of digital low-pass filtering and resampling (decimation) [Norsworthy et al., 1997, Sec. 1.3].

This thesis deals with a special  $\Delta\Sigma$  modulator topology with optimized circuit complexity and conversion efficiency for dc measuring applications. The proposed structure is called higher-order incremental  $\Delta\Sigma$  converters (may also be referred as charge-balancing  $\Delta\Sigma$  converter) introduced in the next subsection.

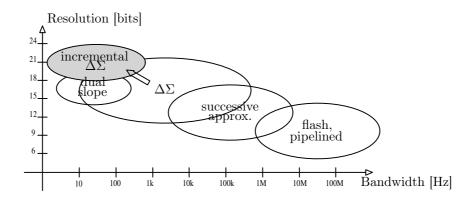

To give an insight into the different applications and different converters used today, and to identify the application area of the proposed architecture, Tab. 1.2 shows different A/D architectures used for different applications ( $\Delta\Sigma$  converter structures discussed in this thesis are typeset in boldface), while Fig. 1.1 shows the targeted resolution and bandwidth requirements of the discussed architecture among typical A/D converters (the group of  $\Delta\Sigma$  converters discussed in this thesis are in the gray ellipse).

Figure 1.1: Applications of A/D converter structures for typical resolution and bandwidth requirements. Gray area represents the architecture discussed in this thesis.

### 1.1 Analog-to-digital Conversion for Measurement Applications

In instrumentation, measurement and sensor/transducer applications, often A/D converters with very high dynamic range are required. Such a typical example is a photodiode, which may produce signal currents between the 1pA and 1 $\mu$ A range, spreading about 6 decades in dynamic range. Similar dynamic range may be required in seizmic measurements. In addition to the high resolution demand ( $n_{\rm bit} \geq 20$ ), these converters also requires high absolute accuracy, including high linearity and negligible offset. Moreover, especially in battery-powered sensor and on-the-field measurement applications, power consumption, thus IC area-consumption must also be kept as low as possible. The only property which is easier to handle is bandwidth, since most of these application operates with dc-signals or low-frequency signals (up to a few kHz).

Among Nyquist-rate ADCs, dual-slope and voltage-to-frequency converters have dominated dc measurement applications for many years. However, as the need to integrate analog circuits into SoC (System-on-a-Chip) environment increased, these converters could not be used, as they usually rely on precise, large elements (such as integrating capacitors), and their technology cannot be easily integrated into low-voltage CMOS environment. In addition, these architectures cannot tolerate high-frequency switching noise originating from the digital circuitry. As RC constant mismatch in CMOS technology may have an implementation error of 20%(!), and in capacitor-ratio a maximum of 0.1% mismatch can be achieved with very careful layout [Johns and Martin, 1997, Chap. 10], the realization of high-resolution Nyquist-rate converters becomes very expensive when resolution exceeds 16 bits, either due to the application of individual laser-wafer-trimming, or due to the higher power- and area-consumption, which originates from the required sophisticated off-line or on-line (self-)calibration methods.

For high-resolution, high dynamic range conversion,  $\Delta\Sigma$  A/D converter may be a good candidate. However, classical  $\Delta\Sigma$  converters, used mainly in telecommunication and consumer electronics applications, are characterized by their signal processing parameters, such as dynamic range and signal-to-noise ratio (SNR), as in these applications usually a

running waveform needs to be digitized continuously, and mainly the spectral behavior of the signal is important. Moreover, these converters are mainly dedicated to applications which can tolerate offset and gain errors. On the contrary, in sensor applications the goal is to digitize individual samples or the average value of a noisy dc signal, and must exhibit an excellent sample-by-sample conversion performance (with very low linearity, offset and gain error).

A third candidate for high-precision dc measuring application is the incremental converter and its various extensions. The first first-order CMOS incremental (or charge-balancing) converter has been introduced in [Robert et al., 1987], achieving 16-bit performance in a low-voltage environment. The converter is based on the  $\Delta\Sigma$  architecture, however, it operates only up to N clock cycles while it performs one conversion. Its operation represents a hybrid between the classical Nyquist-rate dual-slope converter and an oversampling  $\Delta\Sigma$  one. Detailed analysis of its operation, as well as various extensions of the original architecture are discussed in Chapter 2 of the thesis.

This thesis deals with the theoretical and practical aspects of higher-order incremental converters. The operating principles, topologies, specialized digital filter design methods and circuit level issues are all addressed. The theoretical results are verified by showing design examples, simulation results and measurements on implemented circuits. Most of the results discussed in this thesis have been published previously in [Márkus et al., 2004; Temes et al., 2004; Márkus et al., 2003; Márkus, 2003; Márkus et al., 2001].

### 1.2 Structure of the Thesis

The thesis is divided into six chapters.

Chapter 2 discusses the basic operation of the first-order incremental converter, its similarity and differences to the dual-slope and the first-order  $\Delta\Sigma$  converters, and its advantages and disadvantages for dc measurement applications. This chapter also contains detailed analysis of the operation under ideal and non-ideal conditions. It also introduces known extensions to the basic structure.

Chapter 3 and 4 contain the main contributions of this thesis to the topic of incremental converters. Chapter 3 gives the possible extensions of the original architecture to higher-order modulators and discusses their basic properties, while Chapter 4 discusses some more advanced properties of the higher-order converters, addressing practical realization problems and different digital filtering techniques. The theoretical analysis is always verified by simulation results.

Chapter 5 shows design examples and selection guides, with detailed comparison between various architectures. It also contains measurement results on a prototype integrated circuit, which implements a 22-bit incremental A/D converter.

Finally, Chapter 6 gives a short overview of the work and discusses second-order problems to be answered in the future, as well as highlights some novel techniques which may be integrated with the introduced technique to further improve the efficiency of dc measuring A/D converters.

### Chapter 2

## Incremental $\Delta\Sigma$ A/D Converters

This chapter focuses on the prior art of making incremental  $\Delta\Sigma$  converters. It introduces the basic idea, the first-order incremental converter and discusses its operation in details. Some new results regarding to the structure, operation and sensitivity of the first-order incremental converter are also introduced. The different extensions of the introduced architecture found in the literature are also analyzed. The chapter finishes with some concluding remarks about the problems arisen by the basic structure.

### 2.1 First-order Incremental (Charge-balancing) Converter

The first-order incremental converter was first introduced by van de Plassche (1978). He presented a converter with 5-digit + sign-bit resolution ( $\approx$  17-bit resolution), based on a  $\Delta\Sigma$  structure. He implemented his design in bipolar technology, using switched-current sources. Later, Robert et al. (1987) introduced a similar structure with more theoretical details in a low-voltage CMOS environment, achieving 16-bit resolution, naming the converter "incremental  $\Delta\Sigma$  converter". As the first-order incremental converter's operation has many similarity to that of the dual-slope Nyquist-rate converter, first this latter's operation is recalled briefly.

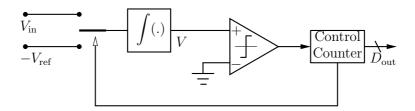

Figure 2.1: Block diagram of the dual-slope converter.  $V_{\rm in}$  is the input signal ( $V_{\rm in} \in [0, V_{\rm ref}]$ ),  $V_{\rm ref}$  is the reference signal, V is the output of the integrator, and  $D_{\rm out}$  is the digital output.

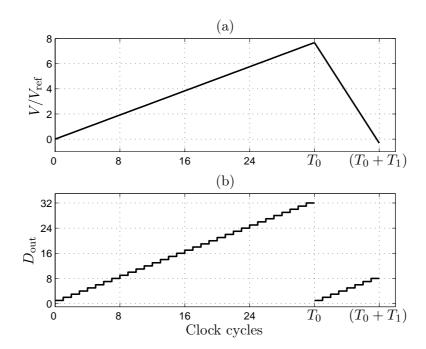

Figure 2.2: Waveforms of a 5-bit dual-slope converter. (a) Normalized output of the integrator  $(V/V_{ref})$ , (b) Output of the counter  $(D_{out})$ .

#### 2.1.1 Dual-slope Converter

The unipolar dual-slope (or charge-balancing) converter (Fig. 2.1) contains an integrator and a comparator [van de Plassche, 1994, Chap. 7]. It operates in a two-cycle mode (Fig. 2.2). In the first cycle, the unknown input signal ( $V_{\rm in} \in [0, V_{\rm ref}]$ ) is entered into the integrator for a given time interval,  $T_0$ . Here,  $T_0$  equals to  $N = 2^{n_{\rm bit}}$  periods of the high-frequency clock signal ( $T_{\rm clk}$ ), where  $n_{\rm bit}$  is the required resolution in bits. At the end of the first cycle, a known reference voltage  $-V_{\rm ref}$  is applied to the same integrator until the output of the integrator reaches (to be more exact, crosses) again 0. The length of this cycle is measured (counted) using the same clock. Let the length of the second cycle be  $T_1$ , during which the counter counts up to  $N_{\rm out}$ . Then, it is readily shown for constant signals that

$$V_{\rm in}/V_{\rm ref} = T_1/T_0 + \varepsilon/2^{n_{\rm bit}} = N_{\rm out}/2^{n_{\rm bit}} + \varepsilon/2^{n_{\rm bit}}, \tag{2.1}$$

where the error (caused by the finite clock frequency)  $\varepsilon$  satisfies  $0 \le \varepsilon < 1$ . Thus, the ratio of the input signal and the reference signal is obtained with  $n_{\text{bit}}$ -bit resolution [van de Plassche, 1994, Chap. 7].

There are several advantages of the dual-slope converter for measurement applications. First, if the integrator is realized as an analog RC-integrator, it can be easily shown that the output is independent of the RC-constant, as this is cancelled by the double integration (this is the main advantage of the converter compared to the single-slope converter). Thus, the main error source is successfully eliminated. Second, the converter can be implemented with a few elements, thus the converter is power- and area-efficient. Additional advantage of the converter is the capability of periodic noise suppression. The unknown input signal

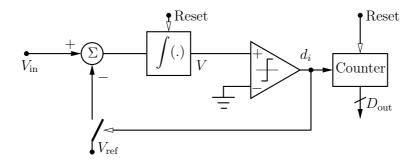

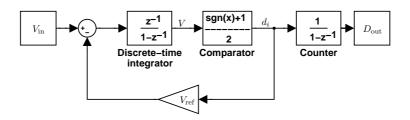

Figure 2.3: Block diagram of the first-order unipolar incremental converter.  $V_{\text{in}}$  is the input signal ( $V_{\text{in}} \in [0, V_{\text{ref}}]$ ),  $V_{\text{ref}}$  is the reference signal, V is the output of the integrator,  $d_i \in \{0, 1\}$  is the one-bit output sequence of the comparator and  $D_{\text{out}}$  is the digital output.

is integrated over a fixed time interval ( $T_0 = 2^{n_{\rm bit}} T_{\rm clk}$ ). If this time interval is matched to the multiple of the fundamental period of a periodic superimposed signal (such as the 50 or 60 Hz line frequency noise coupled from the mains), the integration cancels this additive noise. For example, in the case of  $n_{\rm bit} = 16$ -bit resolution and required suppression of 50 Hz periodic components,  $T_{0,\rm min} = 20$  ms,  $T_{\rm clk} = T_{0,\rm min}/2^{n_{\rm bit}} \approx 0.3 \mu s$ ,  $f_{\rm clk} \approx 3.3$  MHz.

In this latter expression, one of the disadvantages can also be observed, i.e., the conversion time of the converter is extremely slow compared to the converter's clock frequency, especially for high ( $n_{\rm bit} \geq 14$  bit) resolution. The worst-case conversion rate (when the input signal is approaching the reference signal) can be calculated as  $2^{n_{\rm bit}+1}T_{\rm clk}$ . Other disadvantages include offset-errors (can be compensated though, at the expense of longer conversion time or even higher clock-rate), large capacitor and resistor values for proper settling of the maximum output of the integrator. These properties make its implementation in low-voltage CMOS technology difficult.

#### 2.1.2 Unipolar First-order Incremental Converter

The unipolar first-order incremental converter (Fig. 2.3) works somewhat similarly to the dual-slope one. The main difference is that the two cycles (integrating the unknown and the reference signal) are interwoven in time. In the following, a discrete-time model of a converter (can be implemented as a SC circuit) is discussed (see Fig. 2.4). The continuous-time version of the converter is usually referred as integrating  $\Delta\Sigma$  converter [Robert et al., 1987]. First unipolar operation is assumed, i.e.,  $V_{\rm in} \in [0, V_{\rm ref}]$ .

At the beginning of a new conversion, the integrator in the loop and the output counter are both reset. Next, a fixed number  $(N=2^{n_{\rm bit}})$  of discrete integration steps are performed, where  $n_{\rm bit}$  is the required resolution in bits (see the waveforms of Fig. 2.5). Whenever the input to the comparator exceeds zero, its output becomes 1, and  $-V_{\rm ref}$  is added to the input of the analog integrator. After  $N=2^{n_{\rm bit}}$  steps, the next output of the delaying integrator (which is bounded by  $(-V_{\rm ref},V_{\rm in}]$ ) would become

$$V[N+1] = 2^{n_{\text{bit}}} V_{\text{in}} - N_{\text{out}} V_{\text{ref}},$$

(2.2)

Figure 2.4: Discrete-time model of a first-order unipolar incremental converter.  $V_{\text{in}}$  is the input signal ( $V_{\text{in}} \in [0, V_{\text{ref}}]$ ),  $V_{\text{ref}}$  is the reference signal, V is the output of the integrator,  $d_i \in \{0, 1\}$  is the one-bit output sequence of the comparator and  $D_{\text{out}}$  is the digital output.

where  $N_{\rm out}$  is the number of clock periods when feedback was applied. Since V[k] must always satisfy  $-V_{\rm ref} < V \le V_{\rm in} (\le V_{\rm ref})$ , it follows that

$$N_{\text{out}} = 2^{n_{\text{bit}}} (V_{\text{in}}/V_{\text{ref}}) + \varepsilon, \tag{2.3}$$

where  $\varepsilon \in [-1, 1]$ . Generating  $N_{\text{out}}$  with a simple counter at the output of the modulator, one can easily get the digital representation of the input signal.

In an ideal A/D converter, the analog input signal and the digital output signal can be related by the following equation:

$$D_{\text{out}}V_{\text{lsb}} = V_{\text{in}} + qV_{\text{lsb}}, \text{ or}$$

(2.4)

$$V_{\rm in} = V_{\rm lsb}(D_{\rm out} - q), \tag{2.5}$$

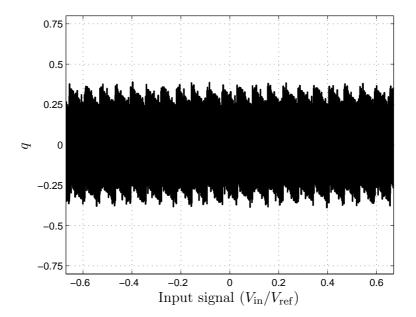

where  $D_{\text{out}}$  is the digital output signal (integer number),  $V_{\text{in}}$  is the analog input signal,  $V_{\text{lsb}}$  is the analog equivalent of one bit, and  $q \in (-0.5, 0.5]$  or  $q \in [-0.5, 0.5)$  is the quantization error. In the case of the unipolar converter discussed above, rearranging Eq. (2.2), one can get

$$V_{\rm in} = \frac{V_{\rm ref}}{2^{n_{\rm bit}}} \left( N_{\rm out} - \left( -\frac{V[N+1]}{V_{\rm ref}} \right) \right).$$

(2.6)

This would imply a  $V_{\text{lsb}} = \frac{V_{\text{ref}}}{2^{n_{\text{bit}}}}$ , output digital code of  $D_{\text{out}} = N_{\text{out}}$  and quantization error of

$$q = -\frac{V[N+1]}{V_{\text{ref}}}. (2.7)$$

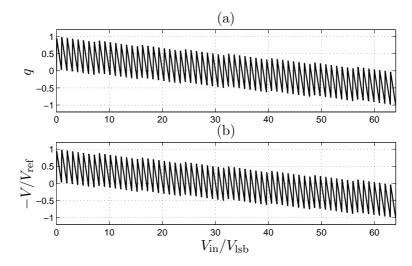

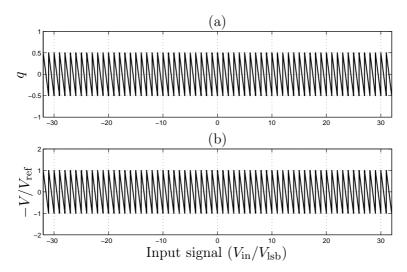

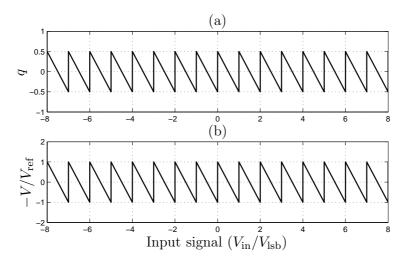

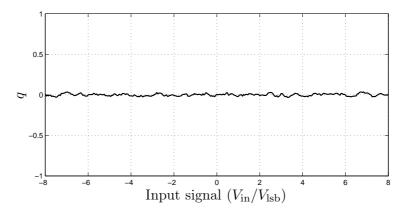

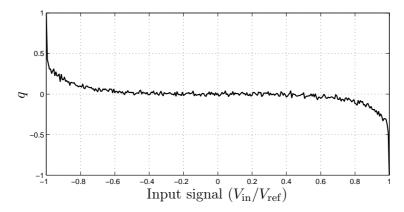

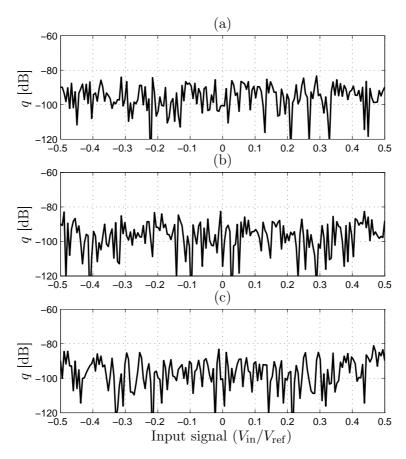

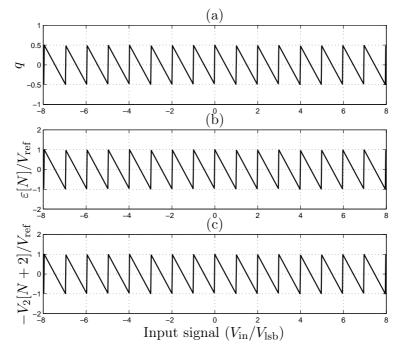

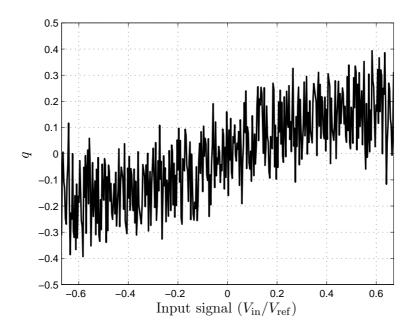

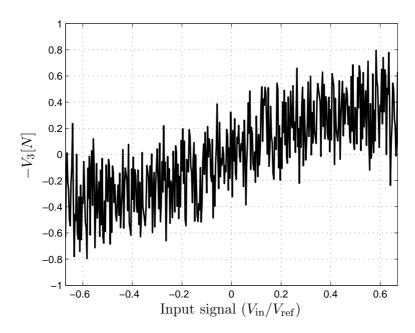

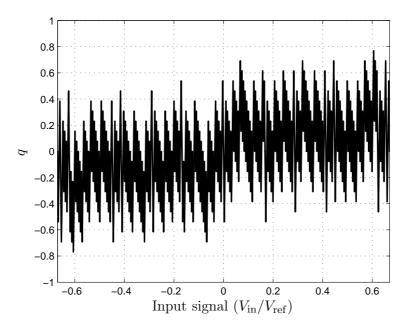

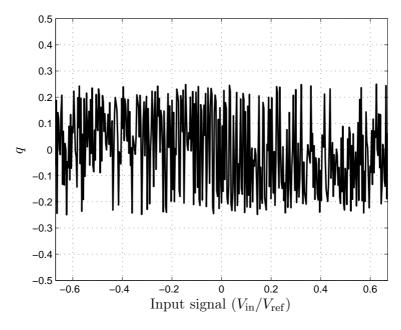

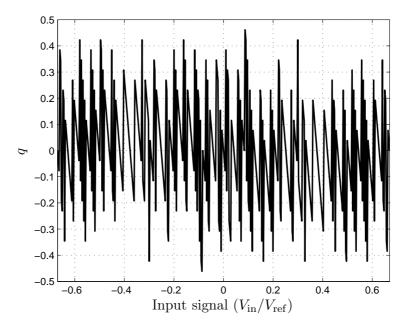

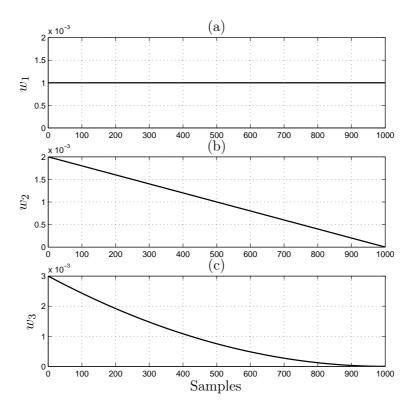

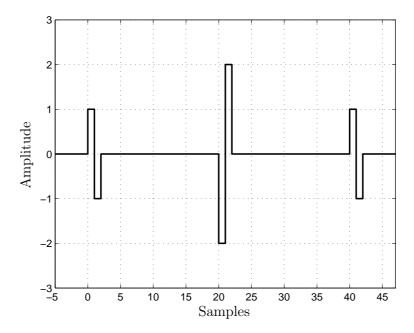

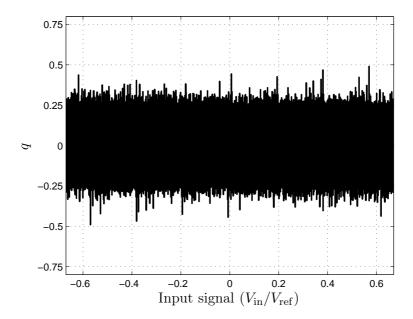

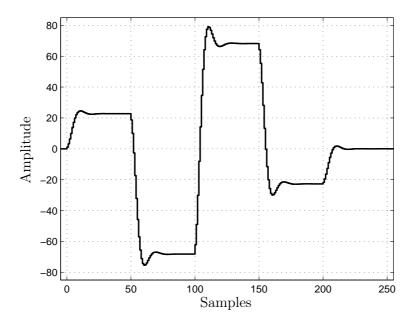

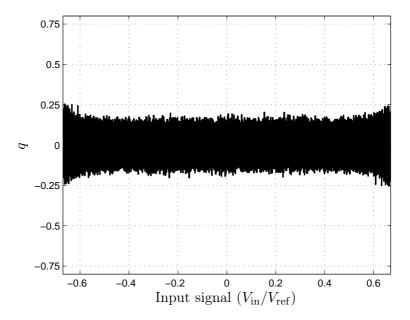

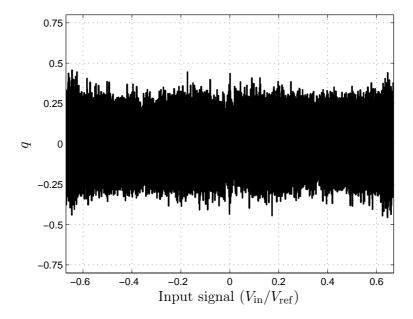

However, as V is limited by  $-V_{\rm ref} < V \le V_{\rm in} \le V_{\rm ref}$ ), the error q is not limited by (-0.5, 0.5], but by (-1, 1]. Simulation results agree well with this statement (Fig. 2.6). One can see (Fig. 2.6(a)) that as the input signal increases, the quantization noise tends to become negative, since its lower limit correlates with  $-V_{\rm in}$  (the integrator's output upper limit is  $V_{\rm in}$ ). Fig. 2.6(b) shows the inverted output of the integrator, V[N+1], which is exactly the same as q.

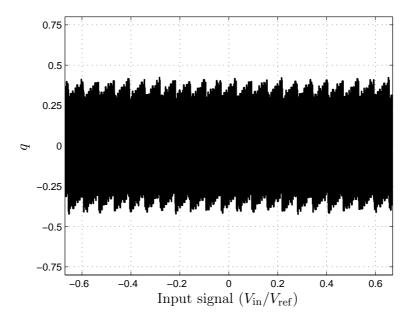

There is a easy way to enhance the operation of the converter: simply operate the converter for one more cycle and count one more. In this case the following happens: in this cycle, the output of the integrator (V[N+1]) contains the inverse of the quantization error (cf. Eq. (2.7)). If this signal is negative (i.e., the quantization error q > 0), the comparator

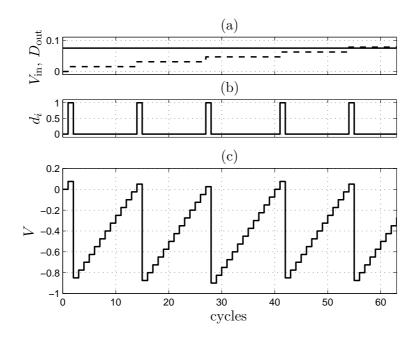

Figure 2.5: Waveforms of the first-order incremental converter. (a) Normalized input signal  $(V_{\rm in}/V_{\rm ref} \in [0,1], \text{ solid line})$  and calculated digital output  $(D_{\rm out}, \text{ dashed line})$ ; (b) output of the comparator  $(d_i)$ ; and (c) output of the integrator  $(V/V_{\rm ref})$ .  $n_{\rm bit}=6$  bits,  $V_{\rm in}=0.075V_{\rm ref}, N_{\rm out}=5$ , indicating a quantized input signal  $N_{\rm out}/2^{n_{\rm bit}}V_{\rm ref}=0.078V_{\rm ref}$ .  $V_{\rm lsb}=0.015625V_{\rm ref}$ , the quantization error is  $q=0.192V_{\rm lsb}$ .

Figure 2.6: (a) Quantization error of a simulated first-order unipolar converter. The error  $q \in (-1,1]$  is not in agreement with its original definition. (b) The inverted output of the integrator  $(V[N+1] = -qV_{\text{ref}})$ .

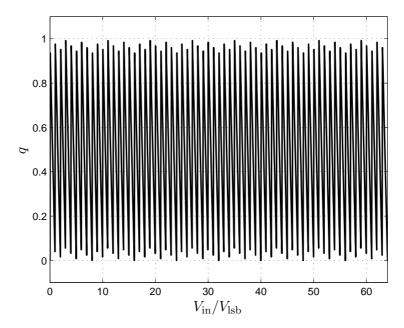

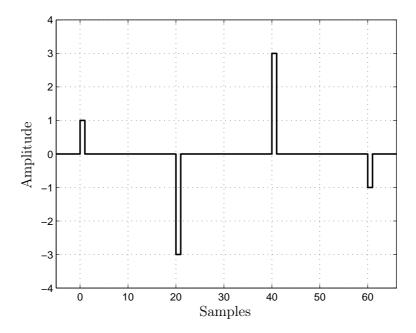

Figure 2.7: Quantization error of a first-order unipolar converter operated through N+1 cycles.

is not triggered, thus outputs zero, which does not change the output of the counter. If the output of the integrator is greater than zero (i.e., q < 0), then the comparator outputs one, incrementing the counter by one. This means that the quantization error will become  $q' = 1 - |q| \in [0, 1)$ , a positive number, less than one. With this operation, the quantization error has been successfully mapped into the interval of [0, 1), which causes only a half LSB shift in the output code. Fig. 2.7 shows simulation results agreeing well with the discussion above.

Similar result may be achieved if the structure is realized so that the input signal is not delayed in the analog integrator but only the feedback signal (this latter delay is required to avoid delay-free loop). Note that any of these cases the expression between the output of the integrator and the quantization error (Eq. (2.7)) does not hold anymore.

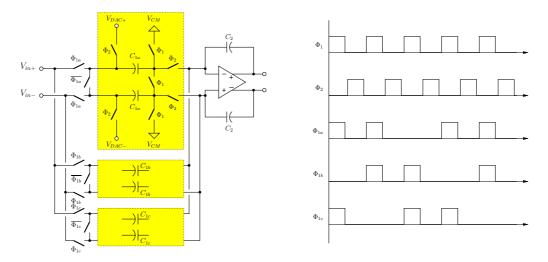

The above analysis about the operation of the unipolar converter was based on the discrete-time model of the first-order converter. This approach models only those delays which are multiple of the sampling time  $(T_{\rm clk})$ , i.e., integer powers of  $z^{-1}$ . However, in a switched-capacitor implementation,  $z^{-1/2}$ ,  $z^{-1/4}$ , etc. delays may also be achieved by dividing the clock signal into many non-overlapping phases and switching the different switches at different phases [Johns and Martin, 1997, Chap. 10] [Robert and Deval, 1988]. By using this technique, it is possible to operate the circuit such that the quantization noise is always in [0,1) [Robert and Valencic, 1985; Robert et al., 1987], but since in this technique information available within one clock period is used to determine the feedback signal, it is not possible to analyze this circuit using z-domain methods. Instead, the operation must be analyzed in the time domain. This method will be illustrated in the next section.

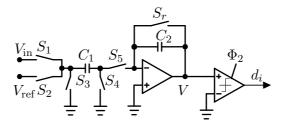

Figure 2.8: Switched-capacitor realization of the first-order incremental converter (without the control logic) operated with four non-overlapping clock-phases.

Figure 2.9: Non-overlapping clock-phases for the operation of the first-order incremental converter.

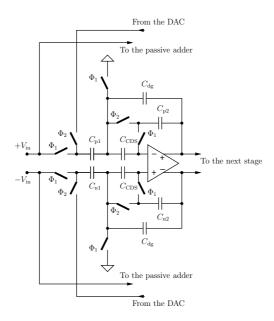

### 2.1.3 Bipolar Operation

The incremental converter is typically operated with bipolar input signals. This extension is rather straightforward: enabling bipolar input signal  $(V_{\text{in}} \in [-V_{\text{ref}}, V_{\text{ref}}))$  and feeding back bipolar reference signal instead of unipolar do the task. However, a detailed analysis in the time-domain is shown here, to introduce the basic operation of switched-capacitor (SC) circuits.

Fig. 2.8 shows a possible SC implementation of the first-order bipolar incremental converter. It consists of a general parasitic-insensitive SC-integrator [Johns and Martin, 1997, Chap. 10] with two input and resetable integrating capacitor, a comparator and control logic (not shown here). Here the switches can be realized as CMOS transmission gates.

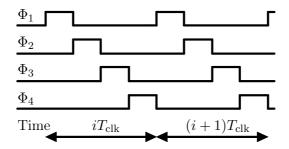

In the following, ideal elements are assumed, with  $C_1 = C_2$ . The circuit needs 4 non-overlapping phase in one clock-period, illustrated in Fig. 2.9.

Before a conversion takes place,  $S_r$  is switched on to reset the integrating capacitor  $C_2$ . Then, in the *i*th cycle the switches are operated as follows. In  $\Phi_1$ ,  $S_1$  and  $S_4$  are closed, while all the other switches are open. This causes charging  $C_1$  to  $V_{\text{in}}$ . In the next phase  $(\Phi_2)$ ,  $S_1$  and  $S_4$  are open and  $S_3$  and  $S_5$  are closed. As  $S_5$  is connected to the virtual ground of the op-amp, this phase forces  $C_1$  to discharge. However, this discharging current must flow through  $C_2$ , thus, the charge is transferred to  $C_2$ , causing V to change to

$$V[i,2] = V[i,1] + \frac{C_1}{C_2} V_{\text{in}}, \qquad (2.8)$$

where [i, k] denotes the kth phase of cycle i. During this phase, the comparator is also

enabled. Thus, at the end of this phase it outputs either  $d_i = 1$  if V > 0, or  $d_i = -1$  if V < 0. If  $d_i = 1$ , then  $V_{\text{ref}}$  is subtracted from V by closing  $S_3$  and  $S_4$  during  $\Phi_3$ , then closing  $S_2$  and  $S_5$  to transfer  $-V_{\text{ref}}$  to the output V. Otherwise, when  $d_i = -1$ ,  $V_{\text{ref}}$  is added to the output similarly to the addition of the input signal, i.e., in  $\Phi_3$   $S_2$  and  $S_4$  are closed to charge  $C_1$ , then  $S_3$  and  $S_5$  are closed to transfer this charge to the output. At the end of the cycle,

$$V[i,4] = V[i,1] + \frac{C_1}{C_2}(V_{\text{in}} - d_i V_{\text{ref}}), \text{ i.e.},$$

$$V[i+1,1] = V[i,1] + \frac{C_1}{C_2}(V_{\text{in}} - d_i V_{\text{ref}}).$$

(2.9)

One can see from the analysis above, that within one cycle, two integrations take place, and the sign of the second input  $(\pm V_{\rm ref})$  depends on the output of the first integration. Thus, analysis of this circuit in the z-domain (assuming that one sample interval is T, consisting of these four cycles) is not straightforward.

A significant difference between the model used for the unipolar operation (cf. Fig. 2.4) and this operation is that it is always assured that during  $\Phi_1$  and  $\Phi_4$  the output of the integrator is always between  $\pm \frac{C_1}{C_2} V_{\text{ref}}$ , if the input signal  $|V_{\text{in}}| \leq V_{\text{ref}}$ . This can be proven by induction.

Let  $V[i,1] \in [-\frac{C_1}{C_2}V_{\mathrm{ref}}, \frac{C_1}{C_2}V_{\mathrm{ref}}]$  (which is true for V[0,1] because of the reset signal). If  $V_{\mathrm{in}} \in [-V_{\mathrm{ref}}, V_{\mathrm{ref}}]$  is added to this signal,  $V[i,2] \in [-\frac{2C_1}{C_2}V_{\mathrm{ref}}, \frac{2C_1}{C_2} + 1V_{\mathrm{ref}}]$ . However, if V[i,2] < 0, then  $C_1/C_2V_{\mathrm{ref}}$  is added to this signal, and if V[i,2] > 0 then  $C_1/C_2V_{\mathrm{ref}}$  is subtracted from this signal during the next two phases. Thus, at the end of  $\Phi_4$ ,  $V[i,4] = V[i+1,1] \in [-\frac{C_1}{C_2}V_{\mathrm{ref}}, \frac{C_1}{C_2}V_{\mathrm{ref}}]$  holds again.

Assuming that the cycle discussed above is repeated up to  $N=2^{n_{\rm bit}}$  cycles, the output of the integrator becomes

$$V = \sum_{i=1}^{N} V_{\text{in}} - \sum_{i=1}^{N} d_i V_{\text{ref}} = N V_{\text{in}} - \sum_{i=1}^{N} d_i V_{\text{ref}}.$$

(2.10)

For simplicity, let  $C_1 = C_2$ . Assuming that the input  $V_{\text{in}}$  is constant and utilizing that V is limited by  $\pm V_{\text{ref}}$ ,

$$-\frac{V_{\text{ref}}}{N} < V_{\text{in}} - \frac{1}{N} \sum_{i=1}^{N} d_i V_{\text{ref}} < +\frac{V_{\text{ref}}}{N}, \tag{2.11}$$

i.e., the difference of the unknown input signal and the lhs of the expression with known terms  $(N, d_i, V_{\text{ref}})$  is limited by an interval, which can be made arbitrarily small by increasing N. Thus, an estimate of the input signal is

$$\hat{V}_{\rm in} = \frac{1}{N} \sum_{i=1}^{N} d_i V_{\rm ref}, \tag{2.12}$$

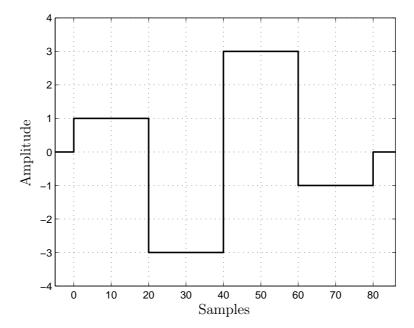

Figure 2.10: (a) Quantization error and (b) inverted output of the analog integrator at the end of the conversion of a 6-bit bipolar first-order incremental converter.

i.e., the digital output can be calculated simply by an up-down counter:

$$D_{\text{out}} = \sum_{i=1}^{N} d_i. {(2.13)}$$

According to the definition of an ideal A/D converter (Eq. (2.4)), the limits in Eq. (2.11) are equal to  $\pm \frac{V_{\text{lsb}}}{2}$ , i.e.,

$$V_{\rm lsb} = \frac{2V_{\rm ref}}{N} = \frac{2V_{\rm ref}}{2n_{\rm bit}}.$$

(2.14)

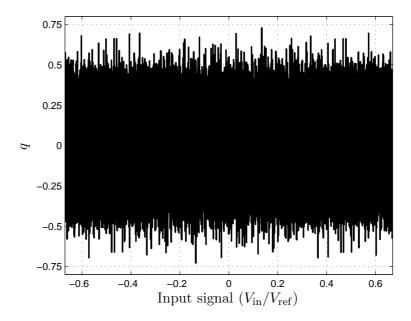

The quantization error q of the conversion can be calculated the following way:

$$q = \frac{\hat{V}_{\text{in}} - V_{\text{in}}}{V_{\text{lsb}}} = \frac{\frac{1}{N} \sum_{i=1}^{N} d_i V_{\text{ref}} - V_{\text{in}}}{\frac{2V_{\text{ref}}}{N}} = \frac{1}{2} \sum_{i=1}^{N} d_i - \frac{1}{2} \frac{NV_{\text{in}}}{V_{\text{ref}}}.$$

(2.15)

Comparing this result with Eq. (2.10), it follows that

$$V[N] = -2V_{\text{ref}}q,\tag{2.16}$$

i.e., the quantization error of the converter is available in analog form at the end of the conversion. This can be used to further refine the digital output: e.g., with minimal effort, the sign of this analog signal can be detected in the next cycle, gaining one more bit precision. More details will be discussed in Sec. 2.2 and in Chaps. 3 and 4.

Fig. 2.10 shows the quantization error (q, Fig. 2.10(a)) and the output of the integrator at the end of the conversion (V[N], Fig. 2.10(b)) for a 6-bit bipolar first-order incremental converter, as functions of the input signal. It can be seen that in this case the quantization error is similar to that of a Nyquist-rate converter, and that Eq. (2.16) is satisfied.

Note that similar operation can be achieved with only two clock-phases. One solution

is (as discussed in the previous subsection) is to operate the circuit for one more cycle to get the correct quantization noise. Although Eq. (2.16) does not hold in this case, it can be proven that

$$V[N+1] = -2V_{\rm ref}q + V_{\rm in}$$

(2.17)

holds. Thus, switching off the input signal for the last conversion cycle (which does not affect the output signal due to the delay in the loop) causes Eq. (2.16) to be true, thus the analog form of the quantization noise may be reused to refine the output. The advantage of the method is less clock phases, which results either in a lower clock frequency and thus less stringent requirements on the op-amp unity gain bandwidth (UGB), or results in faster conversion time. The disadvantage of the method is that it requires bipolar reference signal to make it possible to subtract or add the reference signal during one clock phase ( $\Phi_2$ ).

Instead of switching off the input signal for the last conversion, another solution is to make the signal path from the input signal to the internal quantizer delay-free, either by using non-delaying integrator (which can be implemented with the same hardware and different switching scheme), or by introducing another input signal path, which feeds forward the input signal directly to the input of the internal quantizer. This latter technique will be used for higher-order converters discussed in the next chapter.

#### 2.1.4 Implementation Details

In the detailed analysis of the previous subsection, ideal elements were assumed. In a real converter several non-idealities may degenerate the performance. These are recalled here briefly.

If the circuit is desired for dc measurement application, offset and charge-injection errors need to be kept very small. Offset error is usually caused by the op-amp, while charge injection is caused by the capacitance of the non-ideal switches used in the circuit. To be able to cancel these errors, first the charge injected into the circuit by the non-ideal switches must be made signal-independent. This can be achieved by delaying the operation of signal-flow switches to those which are connected to fix potential. In particular, in Fig. 2.8, switches  $S_1$ – $S_3$  have to be delayed with respect to those of  $S_4$  and  $S_5$  [Johns and Martin, 1997, Chaps. 7, 10], [Haigh and Singh, 1983]. If these charges are signal-independent, then these introduce an additional input-related offset error, which can be cancelled similarly to the error induced by the op-amp.

Signal-independent constant offset signal can be cancelled many ways. One possible way is to do two conversion, the first one is with zero input signal, and the second one with the unknown signal, and then subtracting the result of the first one from the second. However, this solution doubles the conversion time. Another way is to split the conversion to two parts. During the first part the conversion starts as discussed in the previous subsection, then the output of the integrator (V[N/2]) is inverted by the usage of one additional switch, and in the second part of the conversion the input signal is not added, but subtracted from the output of the integrator by using another switching scheme [Robert et al., 1987]. With this inversion, the unipolar offset signal is successfully averaged out from the output. Another method is the usage of auto-zeroing circuit, which cancels the

offset of the op-amp right before the conversion takes place [Robert et al., 1987] [Enz and Temes, 1996].

The analog noise introduced by the switched capacitor circuit is another limiting factor. In switched-capacitor circuits any switched capacitor ( $C_1$  in Fig. 2.8) together with the finite-resistance switches is a noise source with a noise power variance  $\sigma^2 = kT/C$ , where k is the Boltzmann-constant, T is the temperature in Kelvin, and C is the value of the capacitor [Johns and Martin, 1997, Chap. 4]. From this, one can calculate the minimum capacitor size for a circuit with 16-bit resolution and 1V reference voltage. In this case, the variance of the quantization noise (assuming white-noise model) is

$$\sigma_q^2 = \frac{V_{\text{lsb}}^2}{12} = \frac{4 \cdot V_{\text{ref}}^2}{2^{2n_{\text{bit}}} 12},\tag{2.18}$$

i.e.,  $\sigma_q \approx 8.81~\mu\text{V}$ . To make sure that the noise variance from this capacitor is less than this value,

$$\frac{kT}{C} < \sigma_q^2 \tag{2.19}$$

must hold. In this particular case, C > 53 pF is required for this resolution, which is a fairly large capacitor value.

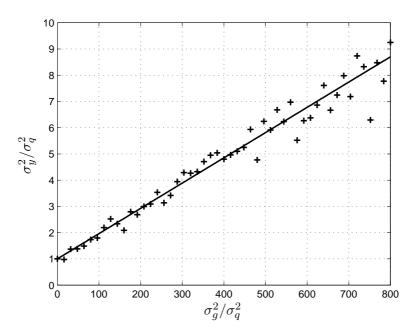

However, in an incremental converter, the input signal is sampled and held by the first capacitor several times and the final result contains the sum of these samples (cf. Eq. (2.10). If the input-referred total noise is Gaussian and has zero mean and  $\sigma_g^2$  variance, the output of the converter will have a variance  $\sigma_g^2/N$ . Note that this simple averaging is called the best linear unbiased estimator (BLUE) of the input  $V_{\rm in}$  with additive zero-mean Gaussian noise. Thus, even higher noise level (even smaller capacitors) may be enabled in the circuit. For example, in [Robert et al., 1987] C = 10 pF capacitors were used. Their input-referred rms noise is about 20  $\mu$ V, but it is divided by  $\sqrt{N} = 2^{n_{\rm bit}/2}$  in the final output, causing an rms error  $20/2^{n_{\rm bit}/2}/V_{\rm lsb} = 0.002$  LSB in a 16-bit converter with 1 V reference. Note that this drastic reduction in the noise contribution is due to the large number of samples averaged during the conversion.

Another important error source in the circuit is the finite op-amp gain, which causes the leakage of the integrator. Robert et al. (1987) found that the error contribution to the output of the integrator with an op-amp gain  $A < \infty$  is

$$E_g = \beta \frac{2^{n_{\text{bit}}}}{A} \tag{2.20}$$

in LSB, where  $0.8 < \beta < 1$  depending on A and  $n_{\rm bit}$ . This implies a relatively large A, e.g., for 16-bit precision A > 100 dB is required, which cannot be easily achieved. Using correlated double sampling [Enz and Temes, 1996] may virtually double the op-amp gain in dB, dropping the op-amp gain requirement to about 60 dB.

Nonlinearities of the capacitors in the circuit were also analyzed and found that capacitors must have a low voltage sensitivity. The circuit is most sensitive to the input sampling capacitor. To achieve the desired linearity, low-voltage sensitivity technology can be used (e.g., metal-metal or poly-poly capacitors with SiO<sub>2</sub> insulator may be used instead

of nitride-oxid) together with design methods (e.g., connecting capacitors with opposite polarity in serial or parallel, to reduce first-order nonlinearity effects).

The introduced converter requires only simple analog and digital circuitry, needs no precision components (as the output is independent of the ratio of the sampling capacitor  $C_1$  and the integrating capacitor  $C_2$ ). Another advantage is that utilizing the four-phase operation discussed in detail in the previous section, only a single reference is required for bipolar operation. This is essential for high-precision conversion. Note that due to the simple circuitry, the area and power requirements are also very modest [Robert et al., 1987] for moderate resolutions. Over the years several paper has reported successful application of the converter [Yufera and Rueda, 1996; Nakamura et al., 1997; Yufera and Rueda, 1998].

The incremental converter is structurally similar to the conventional first-order deltasigma ( $\Delta\Sigma$ ) converter, but there are significant differences: (i) the converter does not operate continuously; (ii) both the analog and digital integrators (in general: memory elements) are reset after each conversion; and (iii) the decimating filter following the  $\Delta\Sigma$ modulator can be realized with a much simpler structure (in this case, with a simple counter).

#### 2.2 Extensions of the First-order Converter

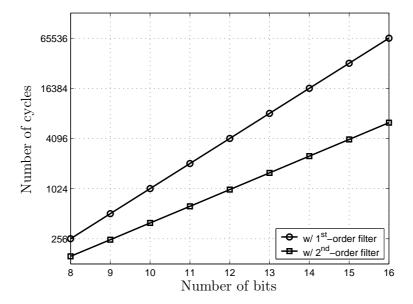

Over the years, the basic idea of [van de Plassche, 1978] and [Robert et al., 1987] has been modified and improved several way, since the fundamental drawback of the original converter is that it must be operated through  $2^{n_{\text{bit}}}$  clock cycles to achieve  $n_{\text{bit}}$ -bit resolution. Thus, the conversion (output) rate is extremely slow compared to the circuit's clock frequency.

The improvements can be classified into two groups: the first one uses the fact that the quantization error is available in analog form at the end of the conversion. Using this signal it is possible to further refine the resolution. Thus, these methods usually perform a coarse quantization with the first-order incremental converter, then make one or more fine quantization cycles using either different or the same hardware. These modifications are described in the next subsection.

Other methods searched for different (mainly higher-order) structures, which are operated in a similar manner, but due to the higher-order architecture lower conversion time can be achieved, similarly to  $\Delta\Sigma$  modulation. These methods are summarized in Sec. 2.2.2 and 2.2.3.

#### 2.2.1 Refining the Quantization Noise

Recalling Eq. (2.16), in a first-order incremental converter the quantization error is available in analog form at the output of the integrator in the Nth or the N+1st cycle. The quantization error  $(q \in [-0.5V_{\rm lsb}, 0.5V_{\rm lsb}])$  is mapped into a signal range  $\pm V_{\rm ref}$  (cf. Fig. 2.10). As this is a large analog signal, it can be easily used as part of a digital correction scheme, to further refine the conversion's resolution. In the related literature, this approach is sometimes called as extended counting conversion.

One of the simplest approach is to use a multi-bit Nyquist-rate converter, which captures this signal and converts it into a fine digital value which may be concatenated to the digital output of the incremental converter. Its one-bit version (i.e., detecting the sign of the residual signal V[N+1] at the end of the conversion) was utilized already in [Robert et al., 1987]. Later, Harjani and Lee (1998) applied a multi-bit Nyquist-rate converter to lower the required number of cycles in the converter and compensate the resolution loss by the multi-bit converter operated at the Nyquist-rate.

More sophisticated ideas use the same hardware to further refine the residue error. Jansson (1995) used successive approximation at the end of the coarse incremental conversion, applying a reduced-by-half feedback signal in every step, and then keeping this signal on or switched off, depending on the output of the comparator. With this extension, the conversion accuracy was greatly improved (16-bit resolution), while conversion time and area-requirements could be well controlled.

Rombouts et al. (2001) introduced an algorithmic (cyclic) converter in which at the end of the incremental conversion the same hardware was used to refine the quantization noise, doubling the residual error by two in every step and use the comparator to detect the next bit.

Mulliken et al. (2002) introduced a two-step algorithmic conversion. In this case, they used the hardware first as a first-order incremental converter, then the residue error at the output of the integrator was resampled and used as an input signal for the next N cycles. Thus, the resulting converter used  $2 \cdot 2^{n_{\text{bit}}/2}$  cycles to achieve a resolution of  $n_{\text{bit}}$  bits. The design resulted in very low power and reduced chip area, applicable to high-density integration such as real-time analog array processing.

#### 2.2.2 Using Different Architecture

Another way to decrease the conversion time is to use different, more complex architecture. In  $\Delta\Sigma$  modulators, there are two ways to increase the achievable SNR in general: one is using multi-stage noise shaping (MASH or cascaded) architecture, the other is to use higher-order modulators. Applications of these techniques for incremental conversion will be discussed in the following.

Robert and Deval (1988) described the use of two-stage (MASH) incremental converter, consisting of two cascaded first-order modulators. In addition, by detecting the sign of the output of the integrator in the second stage at the end of the conversion, an extra bit of resolution was obtained. Using a 2-stage architecture, the number of clock periods required for 16-bit accuracy was reduced to N=362 (or N=257, if the sign of the last integrator's output was used to pick up an extra bit) from the much larger value  $2^{16}$  needed for the first-order converter. As the circuit cancels the outputs of cascaded stages, it is sensitive to circuit non-idealities such as component mismatches and finite op-amp gains. A similar solution, based on a modular architecture and extended to higher-order MASH structures was proposed in [Nys and Dijkstra, 1993].

#### 2.2.3 Higher-order Modulators

Another way of extending the resolution of incremental converters is to use higher-order single-stage modulators. Even though some commercially available converters [Analog, 2004; Burr-Brown, 2004; Cirrus, 2004; Linear, 2004] may use such structures, their theory and design methodology seems to be unavailable in the open literature. These products are sometimes referred as charge-balancing  $\Delta\Sigma$ , one-shot or one-cycle  $\Delta\Sigma$ , or no-latency  $\Delta\Sigma$  converters. An example of the few relevant publications is [Johnston, 1991], however it is mainly a data sheet without detailed description of the operation.

A similar approach was introduced in [Lyden, 1993], and [Lyden et al., 1995]. The idea was here to extend the first-order converter to higher-order one by matching the analog processing of the feedback signal in the modulator with the digital filter following the modulator. The idea required precise matching between the analog and digital coefficients or required longer conversion cycle to compensate for the mismatch errors. As this technique is very similar to the one proposed in this thesis, it is analyzed in detail in Sec. 3.2.2.

The next two chapters of the thesis deals with the theoretical operation and properties of higher-order incremental converters. They also address the most relevant practical problems arising from circuit non-idealities, giving several solutions for the different limitations.

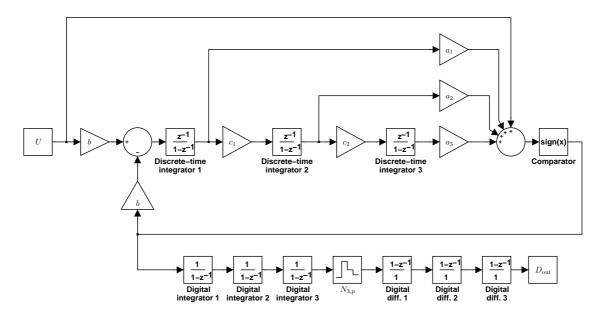

## Chapter 3

# Extensions to Higher-order Architectures

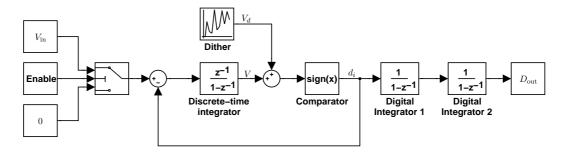

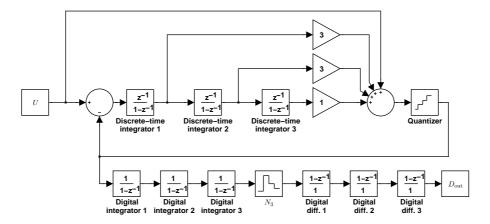

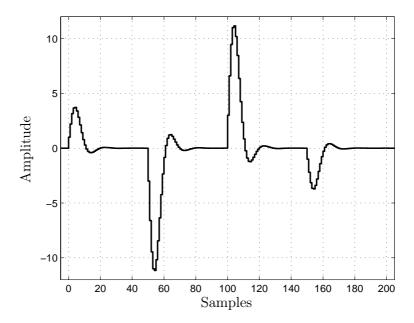

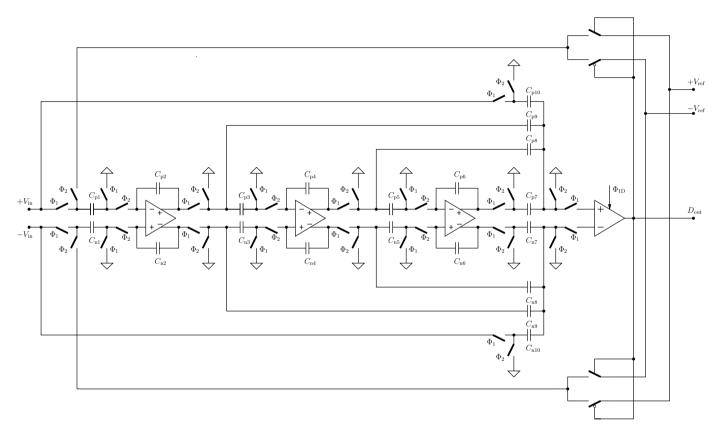

This chapter and the next one focus on the new theoretical results achieved in the field of incremental converters. This chapter consists of two sections. In the next section, the first-order incremental converter is modified with higher-order filtering and dither. Then, three different extensions of the original architecture to higher-order modulators are analyzed in Sections 3.2.1, 3.2.2 and 3.2.3. Many basic properties of the structures are discussed, and at the end of the chapter a comparison of the proposed extensions are given.

## 3.1 First-order Modulator with Higher-order Filtering

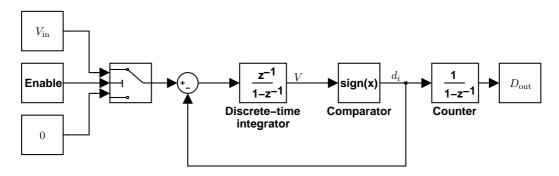

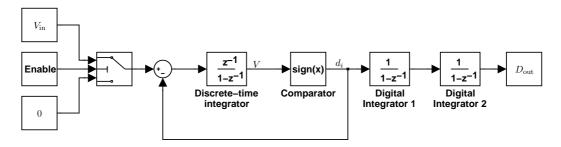

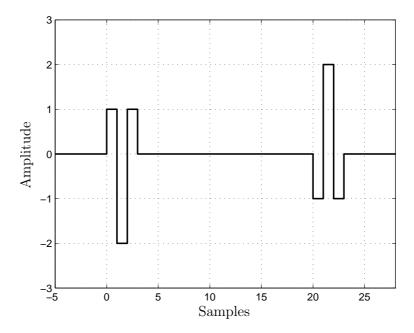

Consider the bipolar first-order incremental converter, consisting of a first-order modulator and a counter. Its bipolar model used for simulations is shown in Fig. 3.1. This circuit models the SC-circuit operated with two clock phases (see the discussion at the end of Sec. 2.1.3), up to N + 1 cycles. The Enabler block is used to disable the input signal for cycle N + 1, to ensure the validity of Eq. (2.16).

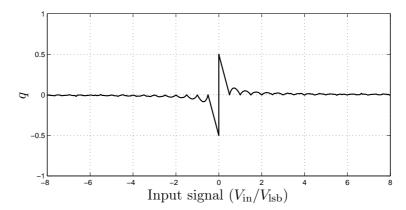

This structure operates similarly to the one realized as SC-circuit with four clock phases (Sec. 2.1.3). Thus, the output of the converter has a quantization error  $q \in [-0.5V_{\rm lsb}, 0.5V_{\rm lsb})$ , and the output of the integrator after the last cycle,  $V[N+2] = -2V_{\rm ref}q$ .

Figure 3.1: Discrete-time model of a first-order bipolar incremental converter.

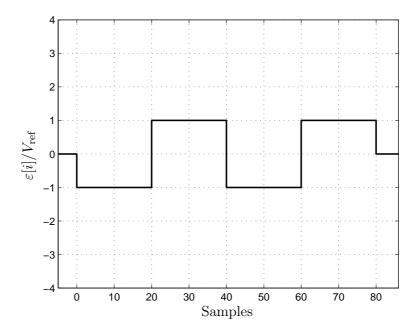

Figure 3.2: (a) Quantization error and (b) inverted output of the analog integrator at the end of the conversion of a 10-bit bipolar first-order incremental converter, around zero input.

This is shown again in Fig. 3.2 for a 10-bit converter, zooming out the converter's error around zero.

As it was discussed in the previous chapter, the converter's biggest drawback is that it requires

$$N = 2^{n_{\text{bit}}} + 1 \tag{3.1}$$

cycles to achieve  $n_{\rm bit}$ -bit resolution. As the architecture is similar to that of a  $\Delta\Sigma$  modulator, a useful idea is to use different filter at the output, similarly to the decimation of  $\Delta\Sigma$  modulators.

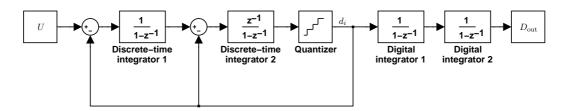

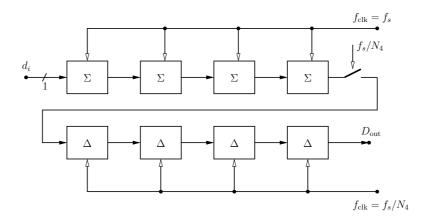

Recalling Eq. (2.13), the output of the first-order converter can be calculated simply by using an up-down counter operated through the first N+1 cycles. As it can be seen in Fig. 3.1, the counter can be modeled as a discrete-time integrator, operated in transient mode. Thus, it realizes an accumulate-and-dump type decimation filter. The output is calculated as

$$D_{\text{out}}[N+1] = \frac{1}{N} \sum_{i=1}^{N} d_i = \frac{1}{N} \sum_{i'=1}^{N} d_{N-i'},$$

(3.2)

switching to z-domain yields

$$D_{\text{out}}(z) = \frac{1}{N} \sum_{i'=1}^{N} z^{-i'} D(z), \tag{3.3}$$

thus, the transfer function becomes

$$H(z) = \frac{D_{\text{out}}(z)}{D(z)} = \frac{1}{N} \sum_{i'=1}^{N} z^{-i'} = \frac{1}{N} \frac{1 - z^{-N}}{1 - z^{-1}},$$

(3.4)

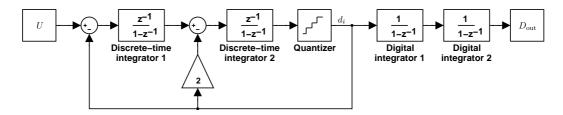

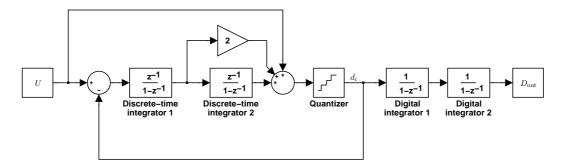

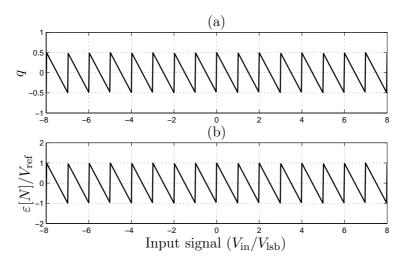

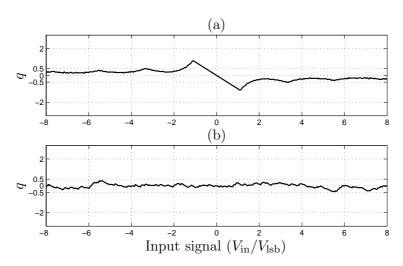

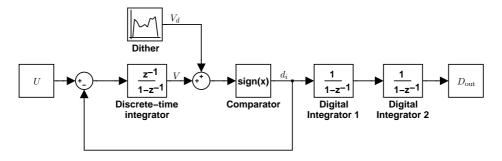

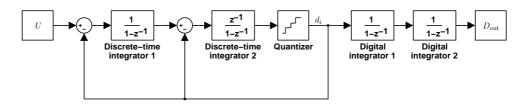

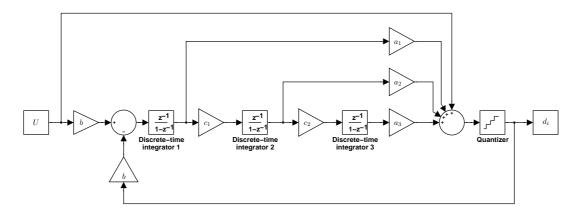

Figure 3.3: Model of a first-order incremental converter with two digital integrators at the output.

and its frequency-response is (using  $z = e^{j\omega T_{\rm clk}}$ )

$$H(f) = \frac{\operatorname{sinc}(fNT_{\text{clk}})}{\operatorname{sinc}(fT_{\text{clk}})} = \frac{\operatorname{sin}(\pi fNT_{\text{clk}})}{N\operatorname{sin}(\pi fT_{\text{clk}})}.$$

(3.5)

This filter has zero dB attenuation at dc and at the multiples of  $f_{\rm clk} = 1/T_{\rm clk}$ , and has multiple zeros at the output rate of  $1/(NT_{\rm clk})$  and at its harmonics (except where the harmonics coincide with  $1/T_{\rm clk}$ ). It is commonly called as first-order digital sinc-filter.

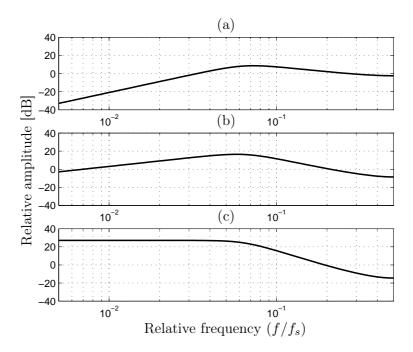

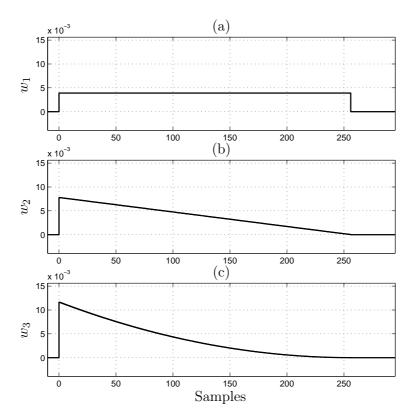

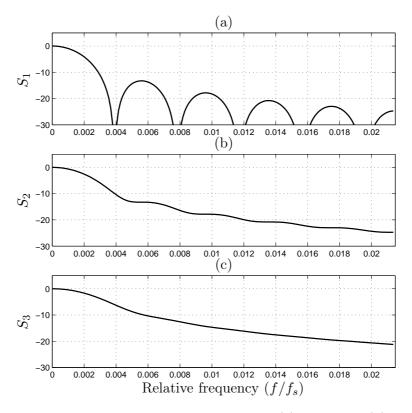

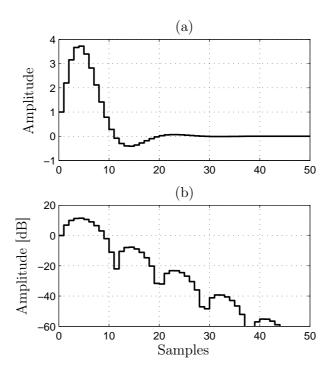

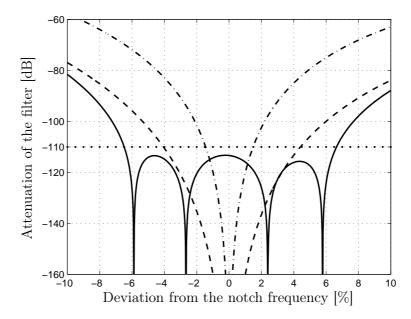

#### 3.1.1 Analysis of Higher-order Filters

Decimation filters following  $\Delta\Sigma$  modulators in  $\Delta\Sigma$  A/D converters usually consists of a higher-order sinc-filter, which decimates the signal output rate to about four times the Nyquist-rate, and final output rate is achieved by either half-band or other FIR-filters [Norsworthy et al., 1997, Sec. 1.3 and Chap. 13]. First-order digital sinc-filters (like the one discussed above) was in use at a time when it was important to save digital hardware [Candy, 1974]. Later Candy et al. (1976) analyzed the application of second-order sinc-filter at the output of the first-order  $\Delta\Sigma$  modulator. Also, a good tutorial about this topic was published in [Candy, 1986]. This tutorial lead to the conclusion that the best trade-off in decimator filter design for  $\Delta\Sigma$  applications is to use  $L_a$  + 1st order filter for an  $L_a$ th-order modulator and decimate the output rate to four times the Nyquist-rate. This rule is still widely used for decimator design, especially since very hardware-efficient implementation techniques (cascaded integrators and comb (CIC) filters) exist [Hogenauer, 1981] [Norsworthy et al., 1997, Sec. 1.3 and Chap. 13].